| EECS150      | Name  | 1 Cal Lines               |

|--------------|-------|---------------------------|

| Midterm2     | Name_ | 130 (unus)                |

| 3/23/06      | SID_  | by Philip Godoy & Friends |

| Spring 2006  |       |                           |

| Prof. Pister |       | Jack Chu                  |

|              |       | Brian Gawalt              |

|              |       | David T. Lih              |

|              |       | Guang Yang                |

|       | Mean / May Poss |

|-------|-----------------|

| 1     | 4.68 15         |

| 2     | 5.65 /15        |

| 3     | 11.96 /20       |

| 4     | 7.46 /15        |

| 5     | 10,53 /20       |

| 6     | 4.69 /10        |

| 7     | 8,54 /15        |

| Total | 53.51/100       |

1. (5 points)

a. In an 8 bit 2s complement number system, what is the representation of -3? -127?

b. Using a standard 4 bit 2s complement representation, write down 3-5 and solve.

$$\frac{-0011(3)}{-0101(5)} = \frac{0011(3)}{-1110(2)}$$

$$\frac{-0101(5)}{-1110(2)}$$

$$\frac{-0101(5)}{-2:1110}$$

c. What are the most positive and most negative numbers that can be represented in a 12 bit 2s complement system, and what are their binary representations?

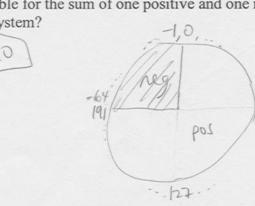

2. (15) Your friend is designing a custom chip with an 8 bit adder. He only needs to represent a few small negative numbers, and sometimes needs to represent numbers a little larger than 127. He decides to change the normal 2s complement representation and allocate ¼ of the wheel to negative numbers and ¾ to positive numbers. He does this by defining that numbers with both b7 and b6 equal to 1 are negative, and all other numbers are positive. The remaining negative numbers are still represented as in normal 2s compelent: -1 is still 8'b11111111 and so on.

a. What is the range of positive and negative numbers that he can represent?

$$2^{4} = 256$$

$$\frac{2^{5}}{4} = 64$$

$$\frac{-64}{4} + 64 + 191$$

$$\frac{-64}{4} = 191$$

$$\frac{-64}{4} = 191$$

b. Is it possible for the sum of one positive and one negative number to overflow in this number system?

64 ×3 192

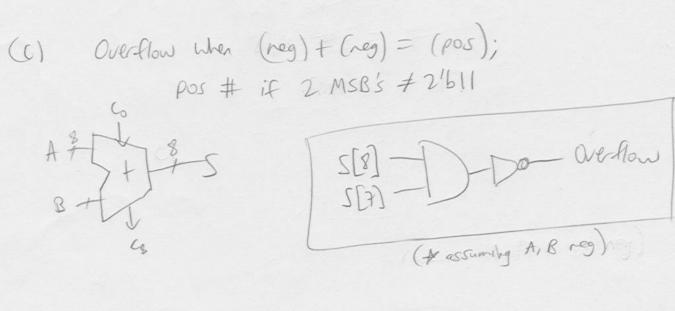

- c. (Prob 2 cont.) Given two negative numbers, implement an overflow detector for detecting when their sum overflows. Use only inverters, AND, and OR gates. You don't need to check that the two numbers are negative.

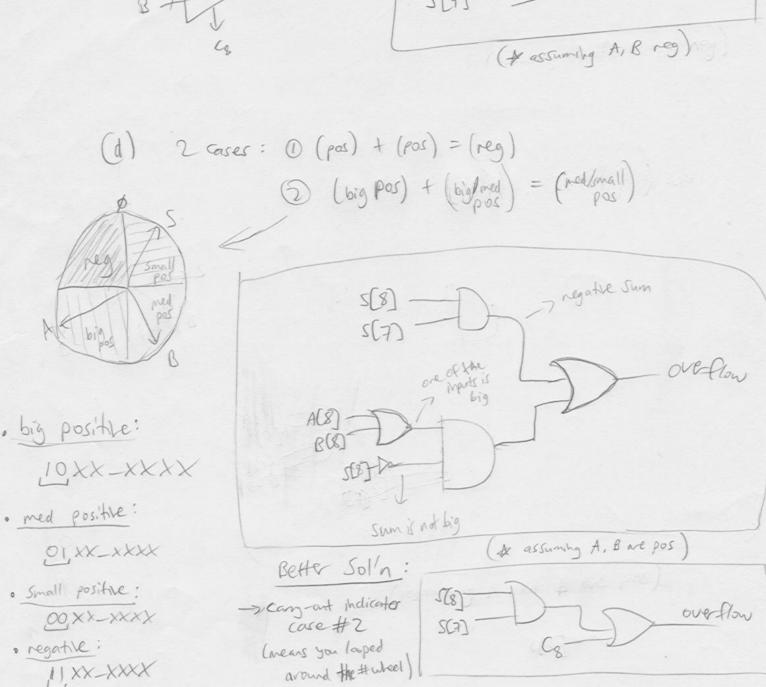

- d. Given two positive numbers, implement an overflow detector for detecting when the sum of two positive numbers overflows. Use only inverters, AND, and OR gates. You don't need to check that the two numbers are positive.

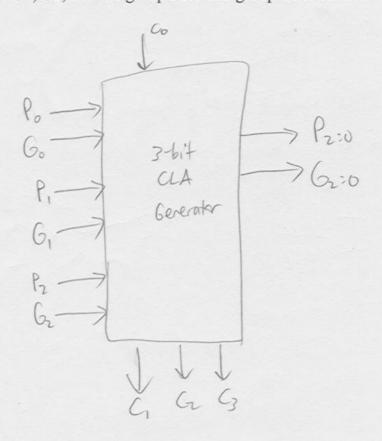

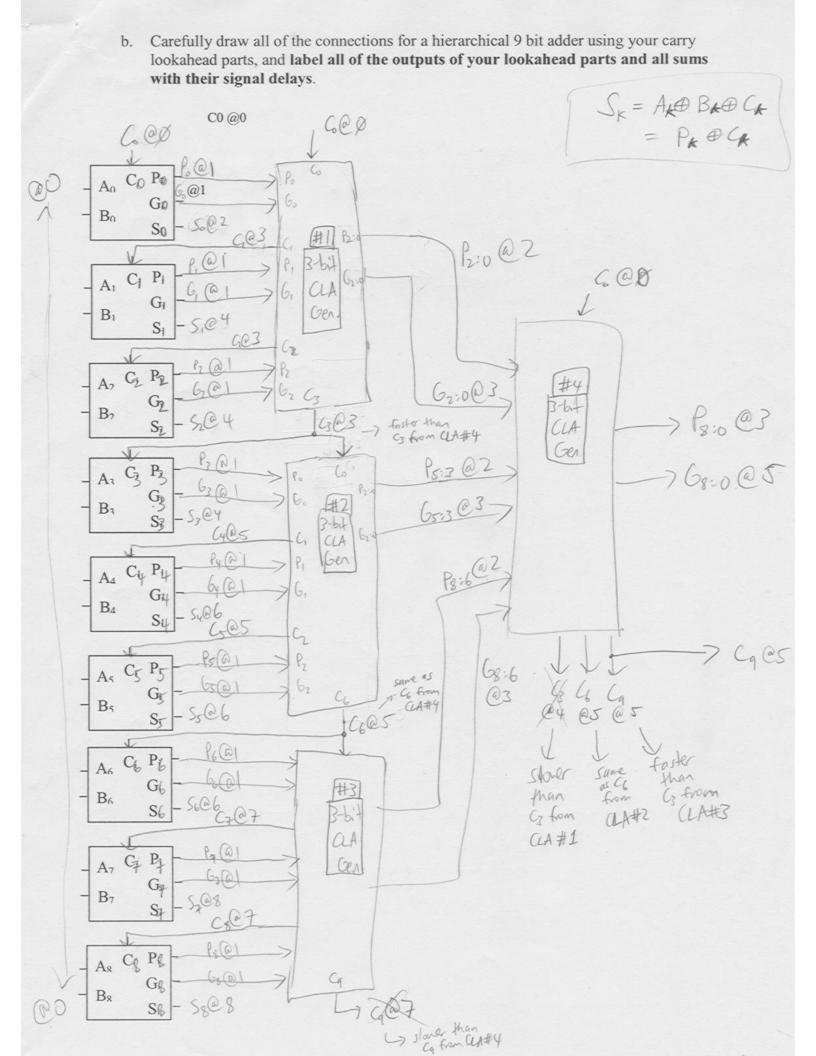

3. (20) In this problem you will design a 9 bit carry lookahead adder:

a. Using inverters and AND and OR gates with arbitrary numbers of inputs, design a 3 bit carry lookahead generator. Assume that single bits generate P and G terms as normal. Your lookahead generator should have inputs Pi and Gi for I=0,1,2, and generate C1, C2, and the group P2:0 and group G2:0 terms.

+ /2 /1 /6

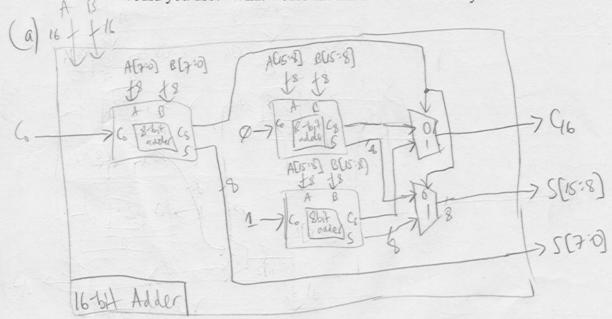

(15) You have implemented an 8 bit ripple carry adder block on an FPGA and measured its worst-case delay at 1ns. You have 2-to-1 MUXes with a delay of 0.1ns.

a. Carefully draw a 32 bit carry-select adder using only your 8 bit ripple carry adder

and 2-to-1 MUXes as building blocks.

What is the worst case delay through your adder?

c. If the delay in your ripple-carry adder is linear in the number of bits, what is the fastest combination of ripple and carry select to implement a 32 bit adder? (i.e. should you use a 4 bit ripple carry adder and more muxes? A 16 bit ripple and fewer muxes?). How many bits in each ripple carry adder, and how many layers of muxes would you use? What would the final worst-case delay be?

-) 32-bit carry-select adder has same structure as above, inst replace the 8 bit adders w/ the 16-bit adders implemented above

| carry-ripple bits | levels of muses | Delay                  |

|-------------------|-----------------|------------------------|

| 32                | Ø               | 32x & = 4ns            |

| 16                | 1               | 16/8+ 1/0 = 21 NS      |

| 8                 | 2               | 8/8+3/10=1.205         |

| 4                 | 3               | 4/8+3/10 = 0.825       |

| 2                 | 4               | 3/8 + 4/10 = 0.65 NS   |

|                   | 5               | 1/8+5/10 = 0.625 AS ZT |

|                   |                 | 1 156                  |

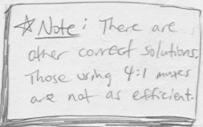

5. (20) Design a 4 bit ripple-carry ALU which implements the following function: When M=0 (arithmetic)

And when M=1 (logic)

|    | M=0 | (arithmetic) |

|----|-----|--------------|

| S1 | S0  | F            |

| 0  | 0   | A            |

| 0  | 1   | A+1          |

| 1  | 0   | A+B          |

| 1  | 1   | A-B          |

| S1 | S0 | F         |

|----|----|-----------|

| 0  | 0  | A NOR B   |

| 0  | 1  | /A NOR /B |

| 1  | 0  | В         |

| 1  | 1  | /B        |

Draw the whole ALU carefully first, and then show the details of the bit slices. You may use inverters, AND, OR, XOR, and MUXes with arbitrary number of inputs.

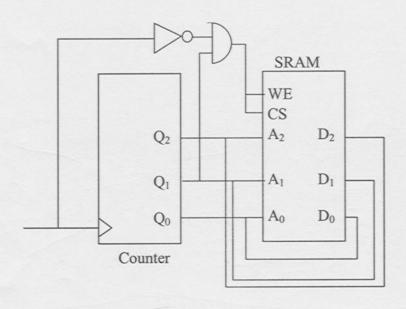

6. (10) In the following circuit, the 8x3 bit SRAM starts with all zeros stored in its memory. The counter is enabled and counts normally. Assume that the clock period is long compared to any SRAM timing constraints. What is the contents of the memory after a few dozen clock ticks? Does it ever change after that?

|   | Add   | MEM (Addr) |

|---|-------|------------|

|   | 000   | 000        |

|   | 001   | 000        |

|   | 0/10  | 000        |

|   | 0 41  | DII        |

|   | 100   | 000        |

|   | 101   | 000        |

|   | 1/1/0 | 110        |

| 1 | 1/1/  | 1111-      |

|   |       |            |

Doesn't change after few dozen clock ticks. 7. (15) Project related questions:

Describe how the N64 communication protocol arbitrates send and receive between the N64 controller and the FPGA.

- challenge/response (FPGA is master, N64 is slave)

- N64 only sends data after FPGA sends it a command

b. Why must active video data to the ADV1794 be clipped? What should the data be clipped to?

- so video data won't be confused W SAV/EAV timing reference signals

- Clipped to range 0x10-0xFD

c. What is the purpose of the IO register between the FPGA and the ADV1794 for the video data?

- ID register is at edge of FAGA

to speed up signal propagation

from FPGA to Video codec

(minimizes risk of timing errors)