## University of California at Berkeley College of Engineering Dept. of Electrical Engineering and Computer Sciences

# EE 105 Midterm I

Spring 2006 Prof. Ming C. Wu Feb. 23, 2006

#### **Guidelines**

- Closed book and notes.

- One-page information sheet allowed.

- There are some useful formulas in the end of the exam.

- The values of common parameters are listed at the beginning of next page.

#### Please use the following parameters for all problems unless specified otherwise:

$$\phi_{n+}$$

= 550 mV,  $\phi_{p+}$  = -550 mV,  $V_{th}$  = 26 mV  $\epsilon_{Si}$  = 11.7,  $\epsilon_{SiO2}$  = 3.9,  $\epsilon_{0}$  = 8.854×10<sup>-14</sup> F/cm,  $q = 1.6 \times 10^{-19}$  C,  $n_{i} = 10^{10}$  cm<sup>-3</sup>.

- (1) Consider a silicon PN junction diode with an N-doping concentration of  $10^{16}$  cm<sup>-3</sup> and a P-doping concentration of  $10^{18}$  cm<sup>-3</sup>. Their cross-sectional area of the diode is 100  $\mu$ m<sup>2</sup>. Assume the reverse saturation current of the diode is  $10^{-14}$  Amp. The diode is forward biased at 0.7V.

- a) [10 pt] Find the dynamic resistance at this bias.

- b) [10 pt] Find the depletion capacitance at this bias.

- (2) Consider a MOS capacitor with a P+ polysilicon gate and an N-doped substrate with a doping concentration of 10<sup>16</sup> cm<sup>-3</sup>. The thickness of the oxide is 20 nm.

- a) [10 pt] Find the threshold voltage.

- b) [10 pt] Which mode is the MOS capacitor in when its gate is biased at 1 V?

- c) [10 pt] What is the maximum capacitance per unit area?

- d) [10 pt] What is the minimum capacitance per unit area?

- (3) [10 pt] For the MOS capacitor in Problem (2), plot the charge density distribution as a function of position when the gate is biased at -2V. Please be as quantitative as possible. Show the positions of all charges, and show the magnitude and polarity of the charges.

- (4) [10 pt] If the P+ gate of the MOS capacitor in Problem (2) is replaced by a metal whose electrostatic potential is 0V. What is the threshold voltage of the new MOS capacitor?

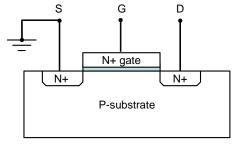

- (5) Consider an N-MOSFET with an N+ polysilicon gate on P-type substrate ( $N_a = 10^{17}$  cm<sup>-3</sup>). The source is grounded, and the drain is biased at 5V. The transistor has a gate length of 1  $\mu$ m, and a width of 10  $\mu$ m. The thickness of gate oxide is 10 nm. For simplicity, assume the channel-length modulation parameter  $\lambda = 0$ .

- a) [10 pt] At what gate voltage does the transistor turn on, i.e., start to have significant current flowing between source and drain?

- b) [10 pt] Find the drain current when the gate is biased at 2V.

### **Some equations**

Mass-action law  $n \times p = n_i^2(T)$

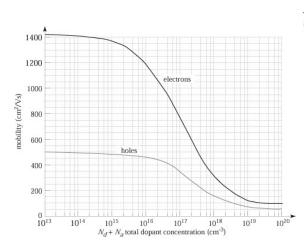

Resistivity:  $\rho_n = \frac{1}{\sigma_n} = \frac{1}{q\mu_n N_{d,eff}}$

Resistance:  $R = \frac{\rho L}{Wt} = \left(\frac{\rho}{t}\right)\left(\frac{L}{W}\right) = R_{sq}\left(\frac{L}{W}\right)$

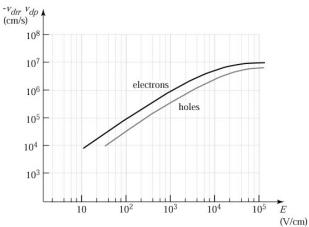

Total current (e<sup>-</sup>):  $J = J_{drift} + J_{diff} = q\mu_{n}nE + qD_{n}\frac{dn}{dx}$

Gauss's law:  $\oint E \cdot dS = \frac{Q}{\varepsilon}$  Q = CV  $E = -\frac{d\phi}{dx}$

Depletion layer:  $X_{d0} = X_{p0} + X_{n0} = \sqrt{\frac{2\varepsilon_S \phi_{bi}}{q} \left(\frac{1}{N_a} + \frac{1}{N_d}\right)} \qquad X_d(V_D) = X_{d0} \sqrt{1 - \frac{V_D}{\phi_{bi}}}$ pn depletion layer capacitance:  $C_j = \frac{qN_a X_{p0}}{2\phi_{bi} \sqrt{1 - \frac{V_D}{\phi_{bi}}}} = \frac{C_{j0}}{\sqrt{1 - \frac{V_D}{\phi_{bi}}}}$

pn diffusion current  $J^{diff} = qn_i^2 \left( \frac{D_p}{N_d W_n} + \frac{D_n}{N_d W_p} \right) \left( e^{\frac{qv_D}{kT}} - 1 \right) i_D = I_S \left( e^{\frac{qv_D}{kT}} - 1 \right)$

Diffusion capacitance:  $C_d = \frac{1}{2} \frac{q I_D}{kT} \tau$

Threshold voltage (NMOS)

$$V_{Tn} = V_{FB} - 2\phi_p + \frac{1}{C_{ox}} \sqrt{2q\varepsilon_s N_a \left(-2\phi_p\right)}$$

$$V_{Tn} = V_{Tn0} + \gamma \left(\sqrt{V_{SB} - 2\phi_p} - \sqrt{-2\phi_p}\right)$$

$$\phi_p = -\frac{kT}{q} \ln \frac{N_a}{n_i}$$

NMOS equations:

$$\begin{split} I_D &= 0, \quad V_{GS} < V_{Tn} \\ i_D &= \frac{W}{L} \mu C_{ox} \bigg( v_{GS} - V_{Tn} - \frac{v_{DS}}{2} \bigg) v_{DS} \big( 1 + \lambda V_{DS} \big), \quad V_{GS} > V_{Tn}, \ V_{DS} < V_{GS} - V_{Tn} \\ i_D &= \frac{W}{L} \frac{\mu C_{ox}}{2} \big( v_{GS} - V_{Tn} \big)^2 \big( 1 + \lambda V_{DS} \big), \quad V_{GS} > V_{Tn}, \ V_{DS} > V_{GS} - V_{Tn} \end{split}$$

MOS capacitances in saturation

$$C_{qs} = (2/3)WLC_{ox} + C_{ov}$$

$C_{ov} = L_DWC_{ox}$

MOS signal parameters:

$$g_{m} = \frac{\partial i_{D}}{\partial V_{GS}}\bigg|_{V_{GS}, V_{DS}} = \mu C_{OX} \frac{W}{L} (V_{GS} - V_{Tn}) (1 + \lambda V_{DS}) \approx \mu C_{OX} \frac{W}{L} (V_{GS} - V_{Tn})$$

$$r_{o} = \left(\frac{\partial i_{D}}{\partial v_{DS}}\Big|_{V_{GS}, V_{DS}}\right)^{-1} \approx \frac{1}{\lambda I_{DS}}$$

$$g_{mb} = \frac{\partial i_D}{\partial v_{BS}} \bigg|_Q = \frac{\gamma g_m}{2\sqrt{-V_{BS} - 2\phi_p}}$$