Professor Oldham

Fall 1999

### EECS 40 — FINAL EXAM

13 December 1999

| Name: | (50   |       |  |  |

|-------|-------|-------|--|--|

|       | Last, | First |  |  |

| Student | ID: |  |

|---------|-----|--|

|         |     |  |

#### **Guidelines:**

- (a) One page of notes allowed (both sides).

- (b) You may use a calculator.

- (c) Do not unstaple the exam.

- (d) Show all your work and reasoning on the exam in order to receive full or partial credit.

- (e) This exam contains 16 pages plus the cover page and 2 sheets of scratch paper included at the end of the exam. You can remove these from the rest of the exam if you wish.

| Problem | Points<br>Possible | Your<br>Score |  |

|---------|--------------------|---------------|--|

| 1       | 20                 | 22            |  |

| 2       | 25                 |               |  |

| 3.      | 30                 |               |  |

| 4       | 25                 |               |  |

| 5       | 25                 |               |  |

| 6       | 20                 |               |  |

| 7       | 25                 |               |  |

| 8       | 30                 |               |  |

| Total   | 200                |               |  |

$$K = 10^{3}$$

$$m = 10^{-3}$$

$$\mu = 10^{-6}$$

$$n = 10^{-9}$$

$$p = 10^{-12}$$

$$f = 10^{-15}$$

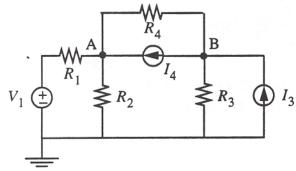

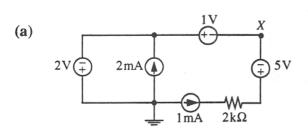

### Problem 1 Nodal Analysis (20 points)

(a) Write 2 nodal equations sufficient to find voltages A and B.

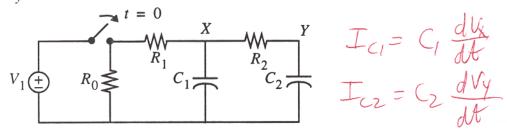

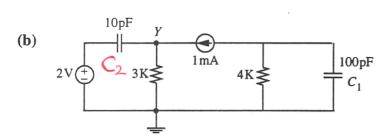

(b) The switch closes at t = 0 (after a very long time open). Write 2 nodal differential equations describing  $V_x$  and  $V_y$ .

(c) What are the values of  $V_x$ ,  $V_y$  at  $t = 0^+$  and  $t \to \infty$ ?

Before switch is closed, no voltage a cross G and Cz. We know voltage across a capacitor is continuous. i.  $V_X(t=0+) = V_Y(t=0+) = 0 V$ .

As

$$t \to \infty$$

, no current flows than  $C_1$  and  $C_2$

$V_X(t \to \infty) = V_Y(t \to \infty) = V_1$

# **Problem 1 Answers**

$$\frac{V_{A}-V_{1}}{R_{1}} + \frac{V_{A}}{R_{2}} + \frac{V_{A}-V_{B}}{R_{4}} - I_{4} = 0$$

$$I_{4} + \frac{V_{B}-V_{A}}{R_{4}} + \frac{V_{B}}{R_{3}} - I_{3} = 0$$

**(b)**

$$\frac{\frac{V_{x}-V_{i}}{R_{1}}+C_{i}\frac{dV_{x}}{dt}+\frac{V_{x}-V_{y}}{R_{2}}=0}{\frac{V_{y}-V_{x}}{R_{2}}+C_{2}\frac{dV_{y}}{dt}=0}$$

(c)

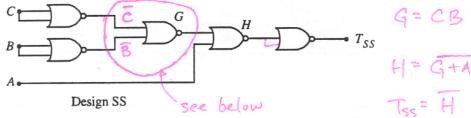

### Problem 2 Nerd Contest (25 points)

In a post-Big Game Nerd Competition, teams from Stanford and UCB were asked to draw logic diagrams to implement the following function:

$$T = A + BC$$

The Stanford team came up with the following design based on NOR gates

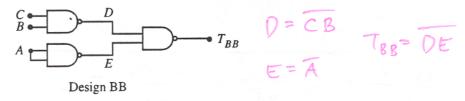

The Berkeley team came up with the following design based on NAND gates:

- (a) Fill out the truth tables opposite to evaluate  $T_{SS}$  and  $T_{BB}$ .

- (b) Do both circuits function as desired?

- (c) Define the unit gate delay of the NOR gates as  $\tau_{NOR}$  and unit gate delay of the NAND as  $\tau_{NAND}$ . Assume the outputs, T, are loaded by similar gates. What is the delay of the Stanford circuit and what is the delay of the Berkeley circuit (in terms of  $\tau_{NOR}$ ,  $\tau_{NAND}$ )?

$$\frac{\overline{c}}{B} = \frac{\overline{c}}{B} = \frac{\overline$$

### **Problem 2 Worksheet and Answers**

(a)

FILL OUT

WITH ZEROS

AND ONES

| A | В | C | G | H | $T_{SS}$ | D | E | $T_{BB}$ |

|---|---|---|---|---|----------|---|---|----------|

| 0 | 0 | 0 | 0 | ( | 0        | 1 | ( | 0        |

| 0 | 0 | 1 | 0 | 1 | 0        | ( | 1 | 0        |

| 0 | 1 | 0 | 0 | 1 | 0        | 1 | 1 | 0        |

| 0 | 1 | 1 | 1 | 0 | 1        | 0 | ( | (        |

| 1 | 0 | 0 | 0 | 0 | 1        | 1 | 0 | (        |

| 1 | 0 | 1 | 0 | 0 | (        | 1 | 0 | 1        |

| 1 | 1 | 0 | 0 | 0 | 1        | ( | 0 | 1        |

| 1 | 1 | 1 |   | 0 | ( L      | 0 | 0 | (        |

both correctly implement A+BC

**(b)**

Function correct? (yes or no?)

T<sub>SS</sub> YES

T<sub>BB</sub> YES

(c) Delay

SS Circuit 4 TNOR

BB Circuit 2 TNANO

# Problem 3 Nerd Contest - Details (30 points) (Independent of Problem 2)

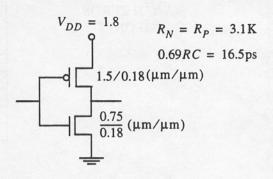

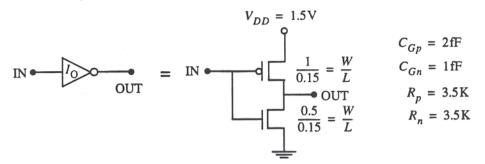

(a) The schematic of a CMOS inverter analyzed in Lecture 25 is shown in the figure below. Note the unit gate delay is 16.5 ps when the inverter drives an identical inverter.

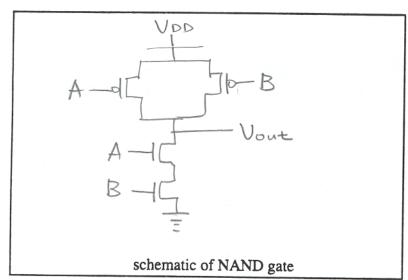

Using the same CMOS technology, you are to design (that means draw the schematic of) a 2-input NAND gate [NOT a layout please!]. Please size the devices for equal worst-case rise and fall times, and use 1.5/0.18 as the p-channel device size.

- (b) Find the input capacitance and the output resistance of such a NAND gate (worst case). Compute the gate delay assuming the NAND gate drives the inputs to identical NAND gates. Ignore drain-bulk and interconnect capacitance.

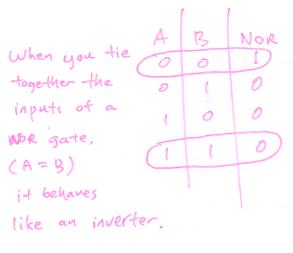

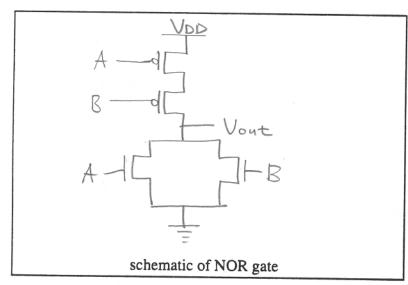

- (c) Now draw the schematic of the NOR gate and indicate device sizes needed to get equal (worst-case) rise and fall times. Again use 1.5/0.18 as the p-channel device size.

- (d) Find the input capacitance and the output resistance of such a NOR gate. Compute the unit gate delay assuming the NOR gate drives the inputs to identical NOR gates. Ignore drain-bulk and interconnect capacitance.

For the inverter in the figure above,

$$16.5ps = 0.69RC \Rightarrow C = (Cap + Can) = 16.5ps / (0.69-3.1kD)$$

$$C = 7.71ff , C \propto Area$$

$$Area (PMOS) = 2 Area (NMOS)$$

$$\therefore Can = 7.71ff \times \frac{1}{3} = 2.57ff (0.75um \times 0.18um)$$

(d)

$$C_{GN} = 1.29 \, \text{FF}$$

(  $0.875 \, \text{um} \times 0.18 \, \text{um} = 1.5 \, \text{um} \times 0.18 \, \text{um}$ )

$C_{GP} = 5.14 \, \text{FF}$

$R = 6.2 \, \text{kel}$

$T = 0.69 \, \times R \times (C_{GN} + C_{GP}) = 27.5 \, \text{psec}$

# **Problem 3 Worksheet and Answers**

(a)

PMOS

$$\frac{W}{L} = \frac{1.5}{0.18}$$

NMOS  $\frac{W}{L} = \frac{1.5}{0.18}$

$$|R_P = 2R_N|$$

$$|NMOS|W = \frac{1.5}{0.18}$$

(b)

$$C_{GP} = 5.14 \text{ fF}$$

$$C_{GN} = 5.14$$

fF

$$R = 3$$

$$R =$$

\_\_\_\_\_K Unit Gate Delay = \_\_\_\_\_pS

(c)

PMOS

$$\frac{W}{L} = \frac{1.5}{0.18}$$

NMOS  $\frac{W}{L} = \frac{0.375}{0.18}$

1. NMOS

$$\frac{1}{2} = \frac{0.375}{0.18}$$

(d)

$$C_{GP} = 5.4$$

fF

$$C_{\rm GN} = \frac{1.29}{100}$$

fF

$$R = 6.2$$

K

R = 6.2 K Unit Gate Delay = 27.5 pS

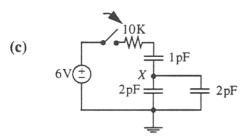

### Problem 4 Simple Circuits (25 points)

$V_X = \frac{3V}{4mW}$ Power delivered by 1mA source =  $\frac{4mW}{4mW}$

$$V_Y = \frac{3V}{7 \text{ mW}}$$

Power delivered by 1mA source =  $\frac{7 \text{ mW}}{1 \text{ mW}}$

Energy stored in  $C_2 = \frac{5 \text{ pJ}}{1 \text{ mW}}$

Capacitors are initially uncharged. Find  $V_X$  long after the switch is

closed. Find peak power  $P_{\text{MAX}}$ delivered by the voltage source.

$$V_X = \frac{6\sqrt{5}}{5} \sqrt{\frac{2}{5}}$$

$$P_{\text{MAX}} = \frac{3.6 \text{mW}}{2}$$

$$V_1 \stackrel{+}{=} X$$

Assume the 4 diodes are perfect rectifiers. (a) What is  $V_X$  when  $V_1 = 5 \text{ V}$ ? (b) What is  $V_X$  when  $V_1 = -5 \text{ V}$ ?

a)

$$V_X = 5$$

b)

$$V_X = 5V$$

(e)

$$X \xrightarrow{3V} 1W \xrightarrow{1V} 2V \xrightarrow{Z} 4V$$

$$X \xrightarrow{1} MA \xrightarrow{1} MA \xrightarrow{2} 2K\Omega$$

$$V_X = \frac{V}{V_Z} = \frac{V}{V_Z}$$

$$V_X = -2 - 1 = -3v$$

$$(1)^{2mA} = (2mA)$$

$$10^{10} \text{ 2mA} = (2mA)(-2v) = -4mW$$

Atsteady-state, capacitor acts litre open circuit.

$$3K \ge 1 \text{Im} A \quad \forall y = (1 \text{Im} A)(3 \text{K}) = 3V$$

$$V_Y = (Im)$$

Voltage across

$$C_2$$

$$2v - V_Y = -1v$$

$$E_{c_2} = \pm (V^2 - \pm (10pF)(-1)^2 = 5pJ$$

By capacitor-voltage division,  $V_X = 6v \left( \frac{1pF}{1pF + 4pF} \right) = \frac{6}{5} = 1.2V$ Bet peak power when capacitors act like short circuitse, so  $P_{\text{max}} = \frac{V^2}{R} = \frac{(36)}{10K} = 3.6 \text{mW}$

$$V_X = 5V$$

for part (a)

$$V_{x} = 3v - 1v + 2v + 4v = 8V$$

8 of 16

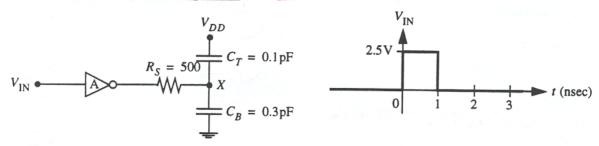

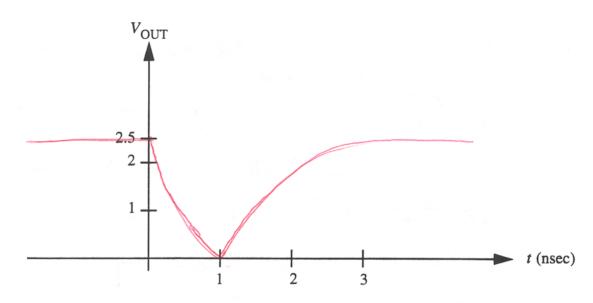

# Problem 5 Inverter Transient (25 points)

olutions

Inverter A is a CMOS inverter with effective output resistance of 1.5K.  $V_{DD}=2.5\mathrm{V}$  and  $V_{Tl}=0.7$ ,  $V_{Th}=1.8\mathrm{V}$ .

The input capacitance is 5 fF,  $V_{\rm IN}$  was zero for t < 0, then a pulse generator (with very low output resistance) produces the input waveform shown above.

- (a) Sketch the general form of  $V_{OUT}(t)$ .

- (b) Calculate  $V_{OUT}$  at t = 0+, t = 1 nsec, and t = 2 nsec.

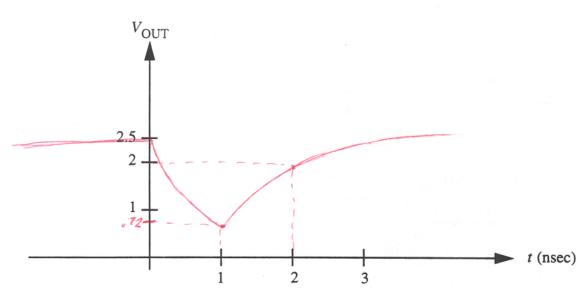

- (c) Re-sketch  $V_{OUT}(+)$  very carefully and neatly.

$$T = RC = (1.5k + .5k)(.3p + .1p) s$$

$$V_{out}(0) = 2.5e^{-9/8} = 2.5V$$

$V_{out}(0) = 2.5e^{-1/8} = .716V$

$V_{out}(2) = 2.5 + (.72 - 2.5)e^{-(2-1)/.8}$

(a)

**(b)**

b.1)

$$V_{\text{OUT}}(t=0+) = 2.5 \text{ V}$$

b.2)

$$V_{\text{OUT}}(t = 1 \text{ nsec}) = ____ 72V$$

b.3)

$$V_{OUT}(t = 2 \text{ nsec}) = \frac{1.99 \text{ V}}{1.99 \text{ V}}$$

(c)

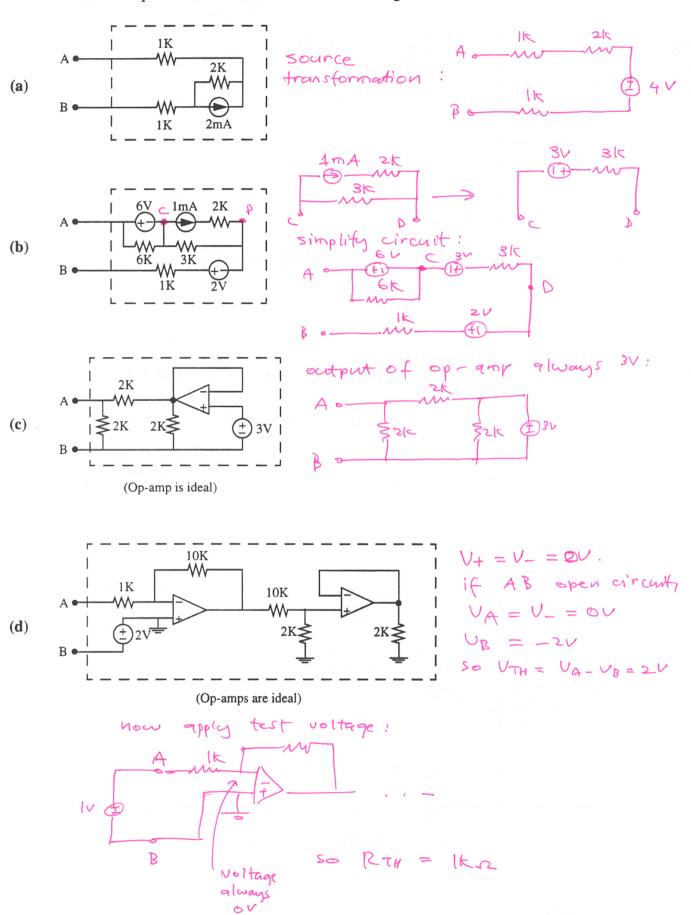

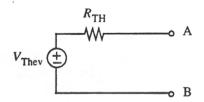

### Problem 6 Thévenin Equivalents (20 points)

Find the Thévenin equivalent circuit for each of the following.

### **Problem 6 Worksheet and Answers**

(a)

$$V_{\text{TH}} = \frac{4 \, \text{V}}{4 \, \text{V}}$$

$$R_{\text{TH}} = \frac{4 \, \text{V}}{4 \, \text{V}}$$

**(b)**

$$V_{\text{TH}} = \frac{4K}{V}$$

$R_{\text{TH}} = \frac{V}{V}$

(c)

$$V_{\text{TH}} = \frac{1.5 \text{ V}}{R_{\text{TH}}}$$

(d)

$$V_{\text{TH}} = \frac{2 \text{ V}}{R_{\text{TH}}}$$

$$R_{\text{TH}} = \frac{1 \text{ K}}{R_{\text{TH}}}$$

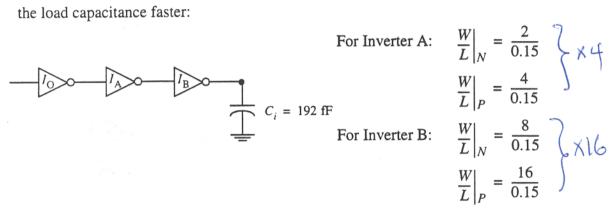

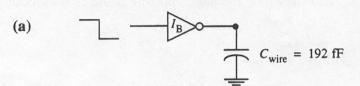

# Problem 7 Capacitive Load (25 points)

We are designing a CMOS logic circuit with the latest devices that use  $L = 0.15 \mu m$ . An inverter schematic is shown for the basic inverter

We need to drive an interconnect wire going across the chip with a capacitance of 192 fF.

- (a) Estimate the stage delay (time to switch the output from zero to  $V_{DD}/2$  with the input going from  $V_{DD}$  to 0) if this inverter drives the wire directly. The 192fF load is connected to the node labeled "OUT".

- (b) Suppose we insert two "buffer inverters" that have larger W/L (and therefore, lower  $R_p, R_n$ ) to drive the load capacitance faster:

Now we suffer 3 stage delays! But let's compute them – maybe it's not so bad. Assume the load on  $I_{O}$  is the gate capacitance of  $I_{A}$  and similarly that the load on  $I_{A}$  is the input capacitance of  $I_{B}$ .

- (b.1) Compute  $C_{Gn}$  and  $C_{Gp}$  for  $I_A$  and  $I_B$ .

- (b.2) Compute  $R_p$  and  $R_n$  for  $I_A$  and  $I_B$ .

- (c-e) Find the unit gate delay for all 3 stages (input step  $V_{DD} \rightarrow 0$  or 0  $V_{DD}$  and output moving from 0 to  $V_{DD}/2$  or  $V_{DD}$  to  $V_{DD}/2$ ).

- (f) Compare total gate delay with that of part (a).

### **Problem 7 Worksheet and Answers**

$$C_{\text{wire}} = 192 \, \text{fF}$$

Unit gate delay =  $\frac{464}{\text{ps}}$

(b) C1x1604 R4x1604

|                                  | Inverter A                | Inverter B                  |

|----------------------------------|---------------------------|-----------------------------|

| $C_{Gn} \\ C_{Gp} \\ R_p \\ R_n$ | 4 +F<br>8 "<br>875<br>875 | 16 fF<br>32 "<br>219<br>219 |

(c)

$$I_A$$

delay

$$,69RC = ,69X3.5KX12FF$$

Unit gate delay =  $29pS$

$$(\mathbf{d}) \qquad \qquad \boxed{I_{\mathrm{A}}} \qquad \boxed{I_{\mathrm{B}}} \qquad \qquad \boxed{I$$

. 69 RC = .69

$$\times$$

875  $\times$  48 + F

Unit gate delay =  $\frac{29 p \text{ S}}{}$

(e)

$$\frac{I_{\rm B}}{\text{delay}} = 192 \text{ fF}$$

$$.69RC = .69 \times 219 \times 192 fF$$

Unit gate delay =  $29pS$

(f) Total of (c) + (d) + (e)

$$87 p^{\varsigma}$$

versus (a)  $464 p^{\varsigma}$  3 delays  $<<1$  delay!

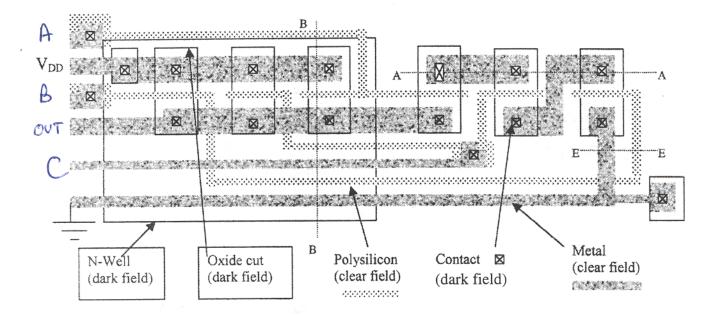

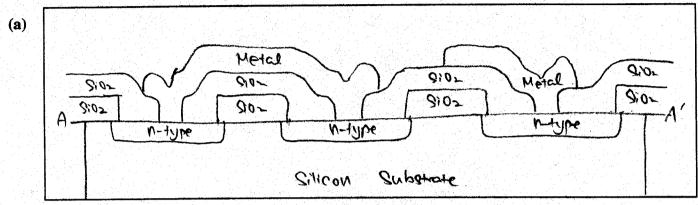

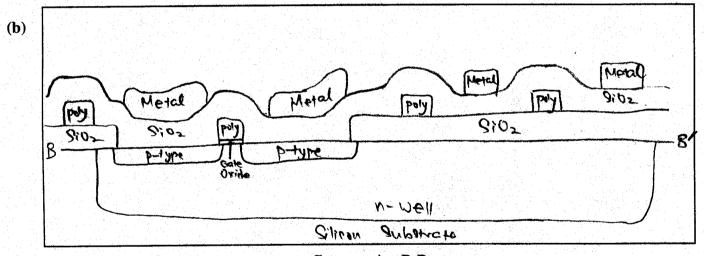

### Problem 8 CMOS Technology (30 points)

The layout of a CMOS logic circuit is shown below. Also shown on the page opposite is the cross-section E-E of the chip.

### The CMOS process is:

- (1) Start: p-Type Si wafer

- (2) Well mask, implant donors

- (3) Grow field oxide 0.5μm

- (4) Pattern oxide (oxide cut for thin oxide)

- (5) Grow gate oxide

- (6) Deposit 0.5μm polysilicon

- (7) Pattern polysilicon

- (8) Two select masks with implants (masks not shown)

- (9) Deposit 0.5μm oxide

- (10) Contact mask, etch oxide

- (11) Deposit 0.5µm metal

- (12) Pattern metal

- (a) In the space provided, draw cross-section A-A. Use E-E as a guide for scale.

- (b) Draw cross-section B-B.

- (c) Label the inputs and outputs of this circuit on the figure above. (Note that there are 6 wires entering from the left and of these, only 2 are labeled, namely  $V_{DD}$  and ground. You are to label the others and use these labels in part d.)

- (d) Write the logic function of the circuit (for example, OUT =  $(A + B) \cdot \overline{C}$ ).

# **Problem 8 Answers**

Cross-section E -- E

Cross-section A-A

Cross-section B-B

(c) (Label figure on opposite page.)

THANKS TO PAUL PARK!

(d) Logic Equation OUT =

$$\overline{A \cdot B \cdot C}$$