# Midterm 1 Professor B. Nikolic

For all problems, you can assume the following transistor parameters (unless otherwise mentioned):

#### **NMOS:**

$$V_{tn} = 0.4, K'_{n} = 115 \text{ uA/V}^2, V_{dsat} = 0.6 \text{V}, lambda = 0, gamma = 0.4 V^{0.5}, 2 phi_{f} = -0.6 \text{V}$$

#### **PMOS:**

$$V_{tp} = -0.4, K'_{p} = -30 \text{ uA/V}^2, V_{dsat} = -1 \text{V}, lambda = 0, gamma = -0.4 V^{0.5}, 2phi_{f} = 0.6 \text{V}$$

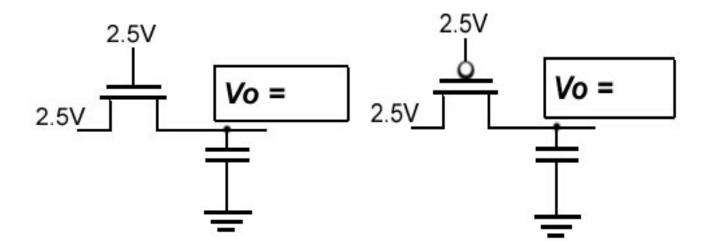

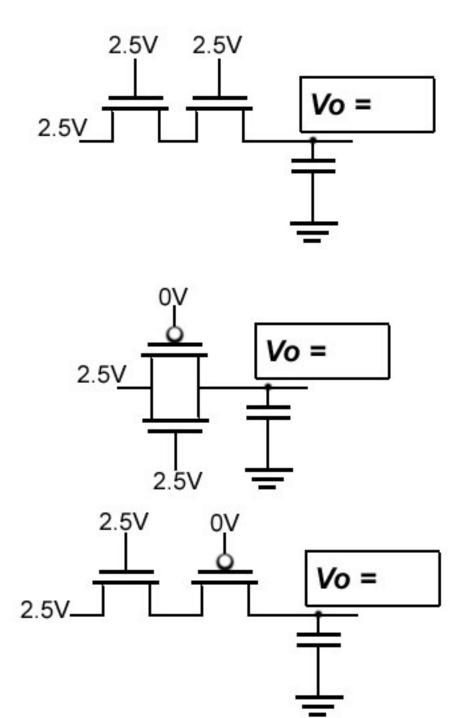

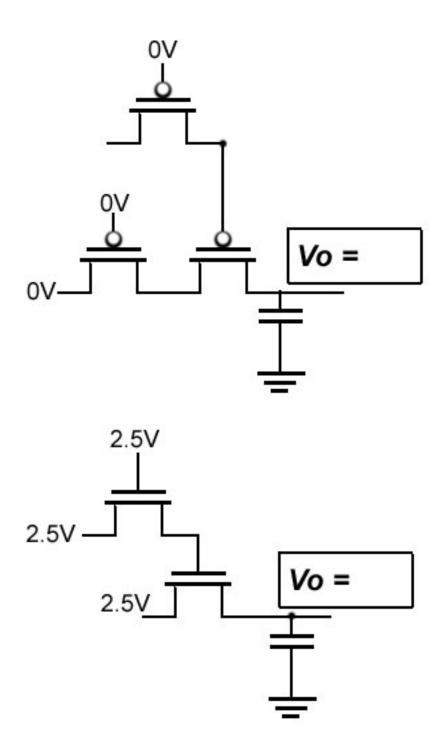

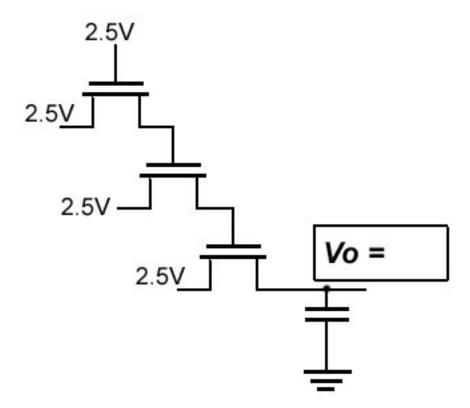

#### PROBLEM 1. MOS transistor as a switch

Find the final value of the voltage  $V_o$ . Assume  $V_{tn} = |V_{tp}| = 0.5V$ . Assume that the capacitor is initially discarged, and ignore subthreshold conduction and body effect.

### PROBLEM 2. Equivalent RC models

In class we modeled the inverter delay by finding its equivalent resistance and capacitance. You are asked to find the equivalent resistance and input capacitiance of a capacitively loaded symmetrically sized inverter.

a) Draw a schematic of how you would measure the equivalent resistance and briefly explain how would you do this.

b) Draw a schematic of how you would measure the equivalent input capacitance of this inverter. Explain the measurement procedure.

c) Does the input capacitance of this inverter depend on its loading? Explain your answer.

d) Does the input capacitance of this inverter depend on the type of transistion (H-L or L-H transition)? If the answer is yes, which one is larger? Explain your answer.

## **PROBLEM 3. Gate Delays**

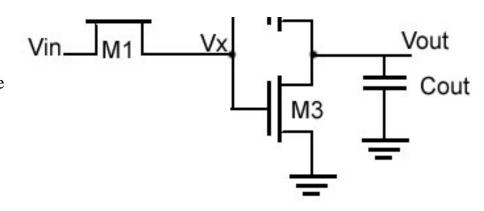

Consider a three-transistor circuit as shown in the figure below. Vdd = 2.5V and input signal switches between 0 and Vdd with

sharp rise and fall times. Use the transistor parameters indicated on the first page of the midterm. Ignore body effect. All transistors are minimum length, L=0.25um. Transistor widths:  $W_2=2$ um,  $W_1=1$ um.

a) Find the  $M_3$  transistor width such that the switching point of the inverter  $(V_m)$  is placed in the middle of the  $V_x$  signal swing.

b) Find the  $t_{plH}$  delay of this circuit.  $C_{ox}=6fF/um^2$ . Overlap capacitances are  $C_o=0.3fF/um$ . Bottom-plate PN junction capacitances are 2fF/um (drain lengths are included). Ignore the sidewall capitances. Ignore the impact of rise/fall times on propagation delay.  $C_{out}=10fF$ .

## **PROBLEM 4. Wire Modeling**

| Consider an isolated 2mm    | long and 1um v    | wide M1 wir   | e over a silicor | substrate | driven by |

|-----------------------------|-------------------|---------------|------------------|-----------|-----------|

| an inverter with zero outpu | ut resistance and | d capacitance | e.               |           |           |

|    | r an isolated 2mm long and 1um wide M1 wire over a silicon substrate cater with zero output resistance and capacitance. |

|----|-------------------------------------------------------------------------------------------------------------------------|

| a) | ) If the wire width is doubled, the delay of this wire will be (circle one):                                            |

|    | More than 2x shorter / Exactly 2x shorter / Shorter, but less than 2x / Unchanged /                                     |

|    | less than doubled / Exactly doubled / More than doubled                                                                 |

| Е  | Explanation:                                                                                                            |

|    |                                                                                                                         |

|    |                                                                                                                         |

| b  | ) If the wire width is halved, the delay of this wire will be (circle one):                                             |

|    | More than 2x shorter / Exactly 2x shorter / Shorter, but less than 2x / Unchanged /                                     |

|    | less than doubled / Exactly doubled / More than doubled                                                                 |

| Е  | Explanation:                                                                                                            |

|    |                                                                                                                         |

c) If the wire thickness is doubled, the delay of this wire will be (circle one):

| More than 2x shorter / Exactly 2x shorter / Shorter, but less than 2x / Unchanged /                             |

|-----------------------------------------------------------------------------------------------------------------|

| Less than doubled / Exactly doubled / More than doubled                                                         |

| Explanation:                                                                                                    |

|                                                                                                                 |

|                                                                                                                 |

| d) If the oxide thickness (between the wire and the substrate) is doubled, the wire delay will be (circle one): |

| More than 2x shorter / Exactly 2x shorter / Shorter, but less than 2x / Unchanged /                             |

| Less than doubled / Exactly doubled / More than doubled                                                         |

| Explanation:                                                                                                    |

|                                                                                                                 |

Posted by HKN (Electrical Engineering and Computer Science Honor Society)

University of California at Berkeley

If you have any questions about these online exams

please contactmailto:examfile@hkn.eecs.berkeley.edu