University of California at Berkeley

# University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Science

EECS 150 Fall 2000 R. H. Katz

## SECOND MIDTERM EXAMINATION

Thursday, 2 November 2000

INSTRUCTIONS – READ THEM NOW! All work is to be done on these pages. Partial credit is given only if we can evaluate your approach: indicate your assumptions and write as neatly as possible. Points are assigned to problems based on our estimate of how long they should take – 1 point equals 1 minute. PACE YOURSELF ACCORDINGLY: it is better to get partial credit on all of the problems than to complete a handful of them. This is a closed book examination. You will need a calculator or other information appliance. You may use a *single* 8.5" by 11" piece of paper (both sides) with prepared notes. Write your name and student ID Number at the top of each examination page.

It is a sad fact of life that cheating sometimes happens. It will not be tolerated. By signing below, you assert that all of the work included herein is your own, and that you understand the harsh penalties that will be imposed should cheating be detected -a 0 on the examination, and a letter of reprimand to your file:

(Signature)

\_\_\_\_\_ SID: \_\_\_\_\_

(Name—Please Print!)

| Question | Points Assigned | Points Obtained |

|----------|-----------------|-----------------|

| 1        | 10              |                 |

| 2        | 10              |                 |

| 3        | 20              |                 |

| 4        | 20              |                 |

| 5        | 20              |                 |

| Total    | 80              |                 |

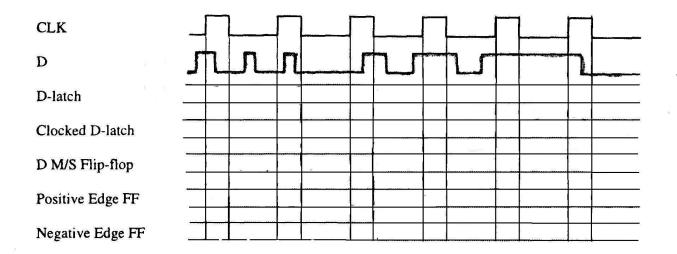

**Question 1.** *Flip-flop Behavior* (10 points)

Consider a D-type storage element implemented in five different ways:

(a) D-latch (i.e., D wired to the S-input and D' wired to the R-input of an R-S latch);

- (b) Clock enabled D-latch;

- (c) Master-Slave Clock Enabled D-Flip-flop;

(d) Positive Edge-triggered Flip-flop;

(e) Negative Edge-triggered Flip-flop;

Complete the following timing charts indicating the behavior of these alternate storage elements. You can ignore set-up and hold time limitations (assume all constraints are meant):

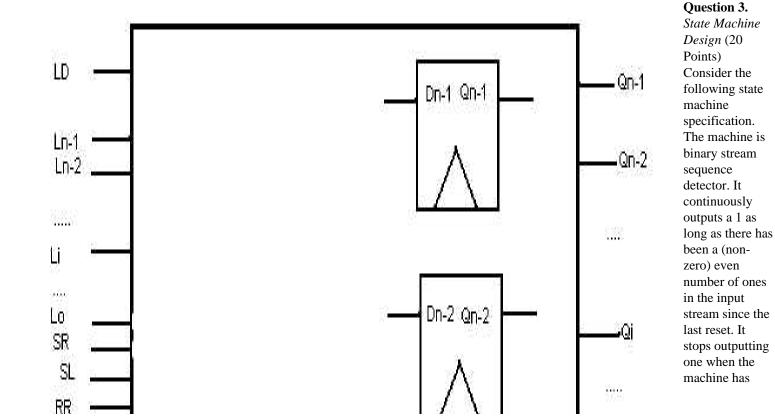

# Question 2. Ultimate Shift Register Design (10 points)

Design the Utlimate N-bit Shift Register, with high order bit  $Q_{n-1}$  and low order bit  $Q_0$ , to the following specification. The register has a synchronous LD input that when asserted causes an external  $L_i$  bit to be loaded into the i<sup>th</sup> storage element. A synchronous Set input and a synchronous Reset input allow all storage elements to be set to a 1 or 0 respectively. The Shift operators are defined as follows.

When none of the control signals are asserted, the register holds its current stat. Internally, the register is made up of conventional edge-triggered D flip-flops with nothing but a D input, a clock, and the Q output. Complete the logic schematic below to implement the shift register. Please draw neatly! HINT: Design general building block that you can personalize and resuse for each register bit.

file:///Cl/Documents%20and%20Settings/Jason%20Raft...20-%20Fall%202000%20-%20Katz%20-%20Midterm%202.htm (2 of 5)1/27/2007 5:35:48 PM

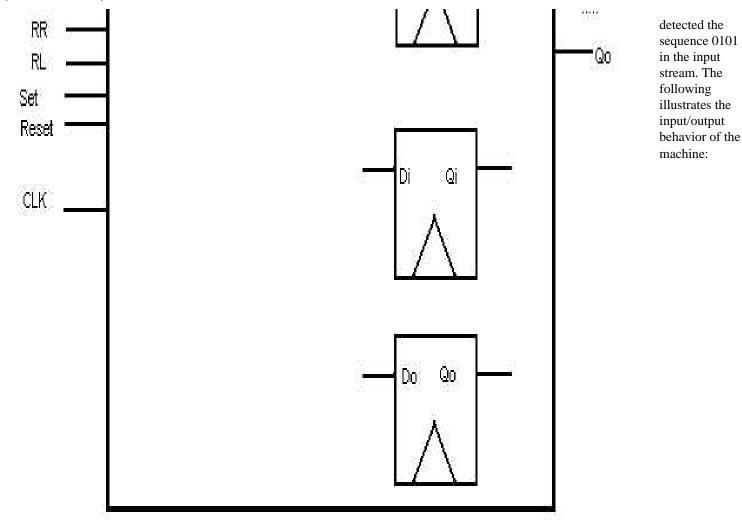

Input:

0 0 1 1 0 1 1 0 1 0 1 1 1 1 1

Output:

0 0 0 1 1 0 1 1 0 0 0 0 0 0 0

Design a MEALY MACHINE for this specification in the boxes below.

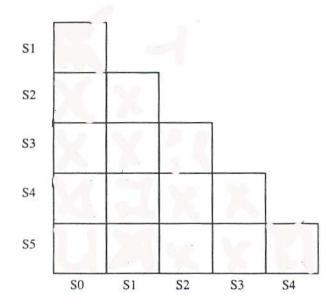

Question 4. State Machine Minimization (20 Points)

Minimize the following six state Moore Machine using the Implication Chart Method.

|               | Next State |            |        |

|---------------|------------|------------|--------|

| Present State | In=0       | In=1       | Output |

| SO            | S5         | S1         | 0      |

| S1            | SO         | S3         | 0      |

| S2            | <b>S</b> 5 | S1         | 1      |

| S3            | SO         | <b>S</b> 4 | 1      |

| S4            | <b>S</b> 5 | S2         | 0      |

| S5            | SO         | S4         | 0      |

Draw a properly labeled and minimized State Diagram below:

#### Question 5. State Machine Timing (20 Points)

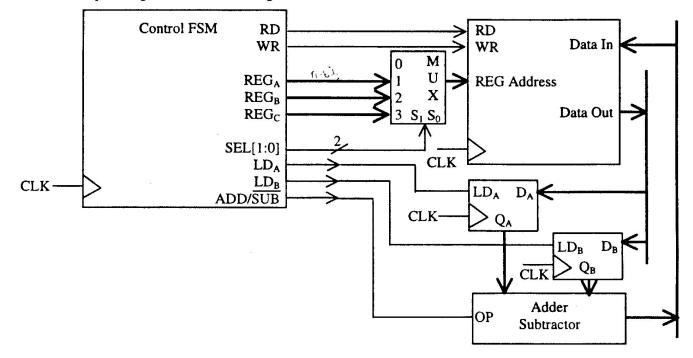

You are to implement a SYNCHRONOUS MEALY MACHINE *state diagram frament* the does the followin. It reads two values from a register file, adds them together, and writes the results back into the register file. The register file can read one value or write one value during any clock period, but not both (this is a so-called single port read/single port write register file). REG<sub>A</sub> and REG<sub>B</sub> are multi-bit read register addresses and

REG<sub>C</sub> a is the write register address. RD and WR control synchronous reading from and writing to the register file respectively. The register file

operates in a single cycle. There are two buffer register with LD control inputs outside the register file. These drive an adder/subtractor circuit, the output of which writes back to the register file.

### The datapath fragment is the following:

Draw the state diagram fragment below, annotating the transitions with the asserted control signals to implement the read/operate/write sequence:

Posted by HKN (Electrical Engineering and Computer Science Honor Society) University of California at Berkeley If you have any questions about these online exams please contact <u>mailto:examfile@hkn.eecs.berkeley.edu</u>